# 全文框架

# 1.低通滤波模块

## 1.1无源滤波器

滤波器可分为有源和无源两类。

无源滤波器有LC和RC两类,LC适用于高频场合,RC适用于低频和功率较小的场合。原因:

- 1.LC滤波器在低频时L很大,绕线电阻很大,造成低品质因数和信号损耗。

- 2.RC滤波器在高频时,R和C要很小(时间常数RC必须要小),此时电阻电容的值精度会对电路有很大影响

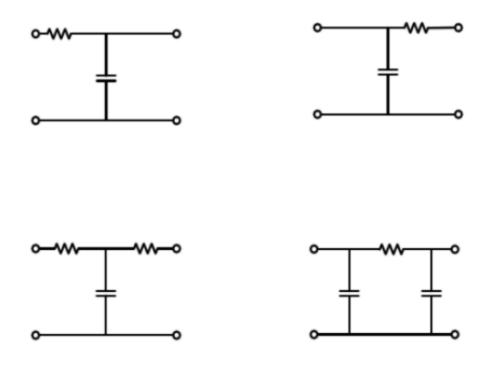

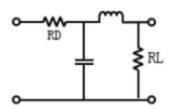

滤波器结构有以下几种:

图 1、L型、倒L型(121843

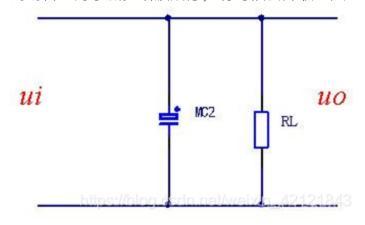

# 1.1.1单电容滤波

在输出端并联一个电容,这种电路较为简单,只有一个一般比较大的电解电容,输出电压随着输出电流变化而变化,外特性比较软,输出特性很差,因此适用于负载电流变化不大的电路,同时负载电流不是很大的场合;为了减少谐波成分,有时候会并联一大一小的电容(小电容的高频特性好,大电容低频特性好)

# 1.1.2 L型RC滤波

系统函数:

$$T(s) = \frac{\frac{1}{sC}}{R + \frac{1}{sC}} = \frac{1}{RCs + 1}$$

幅频特性(时间常数T=RC):

其幅频特性

$$|T(j\omega)| = \frac{1}{\sqrt{T^2\omega^2+1}},$$

(

相频特性

$$\varphi(\omega) = -\tan^{-1}(\omega \mathcal{F})$$

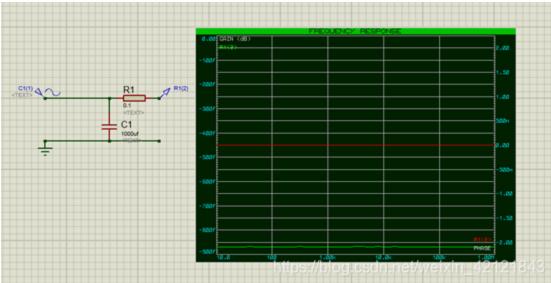

为一阶惯性环节,转折频率为1/T。因此,截止频率Wc为1/RC,在截止频率处,信号衰减为0.707倍,滞后45度。

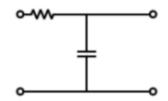

注意R在C之前,否则等效于单电容滤波。

另外注意: RC滤波中R的取值要比负载阻抗低一个数量级, 以忽略其分压的损耗。

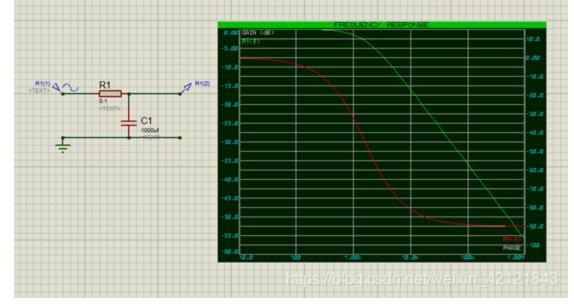

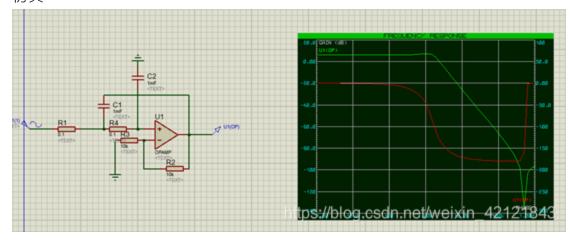

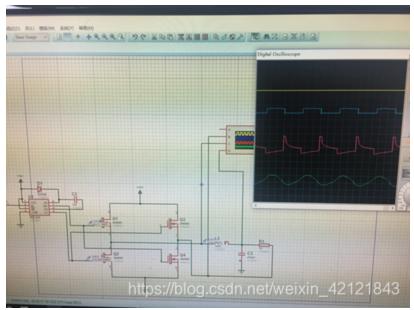

仿真:

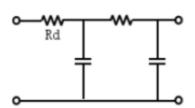

# 1.1.3 π型RC滤波

系统函数:

$$T(s) = \frac{1}{R_d R C_1 C_2 s^2 + [R_d C_1 + R C_2 + R_d C_2] s + 1}$$

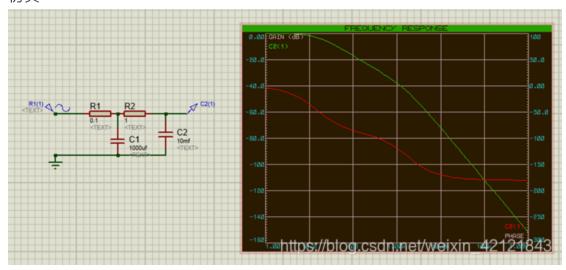

Rd为输入端阻抗,可以看作两个一阶RC滤波合并而成。第一级滤波后减少了交流分量,二级滤波再次减少 纹波。

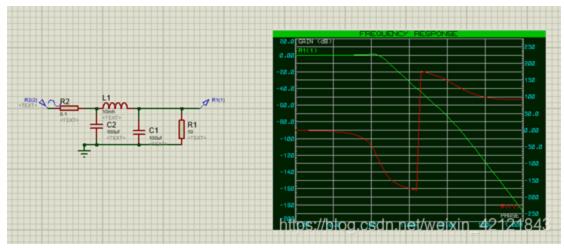

该系统幅频特性为40db衰减,相频特性最终滞后180度。

当RC滤波器阶数高时,分压明显,损耗大。一般不超过三阶。

因RC滤波R的阻值较小,因此负载阻值对其影响小。

仿真:

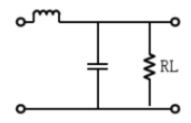

# 1.1.4 L型LC滤波

### 系统函数:

其电压转移函数为

$$T(s) = \frac{\frac{R_L / / (\frac{1}{sC})}{sL + \left[\frac{1}{R_L / / (\frac{1}{sC})}\right]}}{\frac{1}{LC s^2 + \frac{L}{R_L} s + 1}}$$

转换成标准形式

$$T(s) = \frac{\omega_o^2}{s^2 + \frac{\omega_o}{Q}s + \omega_o^2}$$

参数解释:

式中  $R_L$ 为负载阻抗,谐振频率 $\omega_0 = \frac{1}{\sqrt{LC}}$ , $Q = \frac{1}{2\zeta} = R_L \sqrt{\frac{C}{L}}$ 为低通滤波器的品质因数,Q 电路的选择性越强。根据自控理论,若  $Q \ge 0.5$ , $\zeta \le 1$ ,此时滤波器工作于"欠阻尼"状态,若  $Q \le 0.5$ , $\zeta \ge 1$ ,则滤波器工作组"过阻尼"状态,若 Q = 0.5, $\zeta = 0.5$  则滤波器工作组"临界阻尼"状态,若 Q = 0.707, $\zeta = 0.707$ ,超调量<5%,调节时间最短,为最佳阻尼比,电路具有最佳平坦响应。 LC 二阶低通滤波网络参数设计时,若期望最佳平坦响应,应使滤波网络的品质因数 Q 接近 0.707.从品质因数的表达式中,可以看出负载阻抗对于品质因数有很大影响,无源滤波器滤波效果受负载影响极大。根据滤波器阻抗失配选择原理,L型滤波器适用于高频时输入端阻抗较小、负载阻抗较大的场合。

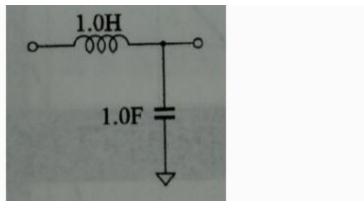

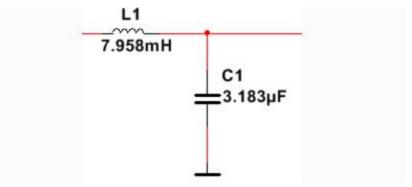

电感电容计算,按照K型滤波器设计,其品质因数为1:

$$L=R/(2\pi \times fc)$$

$$c=1/(2\pi \times fc \times R)$$

式中信号的截止频率 fc,负载阻抗  $R=\sqrt{\frac{L}{c}}$ 。

#### 仿真:

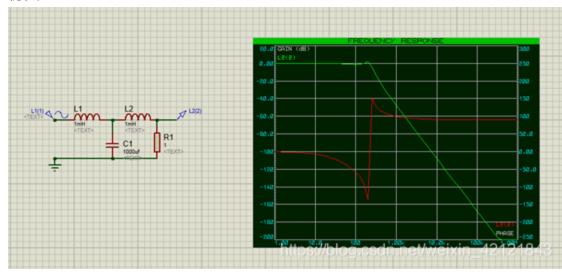

# 1.1.5 倒L型LC滤波

$$T(s) = \frac{R_L}{R_D L C s^2 + L s + (R_L + R_D)}$$

构成二阶震荡环节,幅频特性为-40db衰减,相频特性滞后180度。

效果不及L型LC滤波器,因为输入端阻抗会对其造成影响。适用于输入端阻抗较大,负载阻抗较小的场合。

# 1.1.6 T型LC滤波

$$T(s) = \frac{R_L}{L^2Cs^3 + R_LLCs^2 + 2sL + R_L}$$

为三阶滤波器,幅频特性为-60db衰减。

设计方法:

按照定K型滤波器进行设计

$$L=R/(2\pi \times fc)$$

$$C=1/(\pi \times fc \times R)$$

式中信号的截止频率 fc,负载阻抗  $R=\sqrt{\frac{L}{c}}$

设计时电感一般要相等,这样C两端电压比较平稳,纹波也会很小。T型滤波器适用于高频时输入端阻抗和负载阻抗均较小的场合。

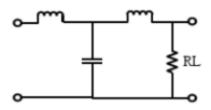

#### 仿真:

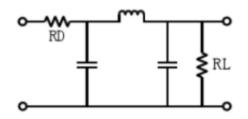

# 1.1.7 π型LC滤波

$$T(s) = \frac{R_{L}}{LC^{2}R_{D}R_{L}s^{3} + LC(R_{D} + R_{L})s^{2} + (2CR_{D}R_{L} + L)s + (R_{D} + R_{L})}$$

性能和设计方法同上,设计时电容相等,可以减少纹波。该滤波器适用于高频时输入输出阻抗均较大的场合

# 1.1.8总结

不管是LC还是RC,L型都比倒L型好,π型和T型相似。阶数越高,滤波器的效果也会越好。

# 附: K型滤波器设计

特征阻抗:指的是当LC回路发生谐振时电容和电压的阻值(此时两者相等),它只与LC的参数有关,计算式为R=√(L/C)

M=(待设计滤波器的截止频率)/(基准滤波器的截止频率)

K= (待设计滤波器的特征阻抗) / (基准滤波器的特征阻抗)

电感值计算: L'= (L\*K) /M

电容值计算: C'=C/(K\*M)

例如: 2阶定K型归一化LPF电路, 截止频率为1/(2\*pi)(pi代表数学圆周率), 特征阻抗为1欧姆。

设计截止频率为1KHz,特征阻抗为50欧姆的LPF定K型滤波器。

$$M = \frac{1KHz}{\left(\frac{1}{2\pi}\right)Hz} \approx 6283.1854$$

$$K = \frac{50\Omega}{1\Omega} = 504$$

$$L' = \frac{L \times K}{M} = 7.958mH4$$

$$C' = \frac{C}{K \times M} = 3.183uF4$$

仿真:

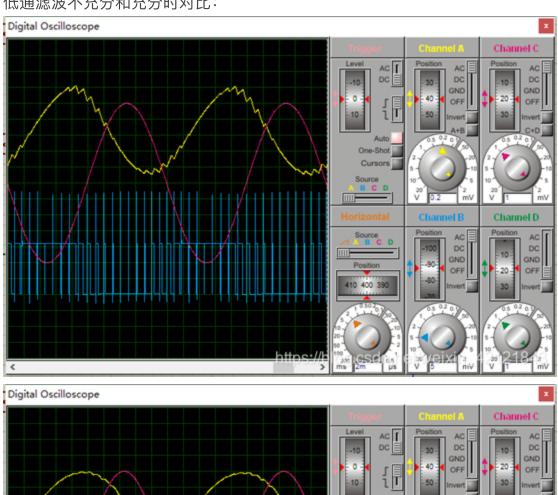

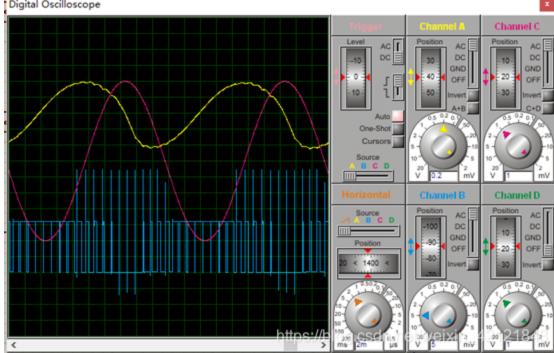

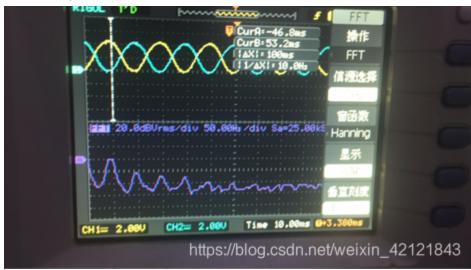

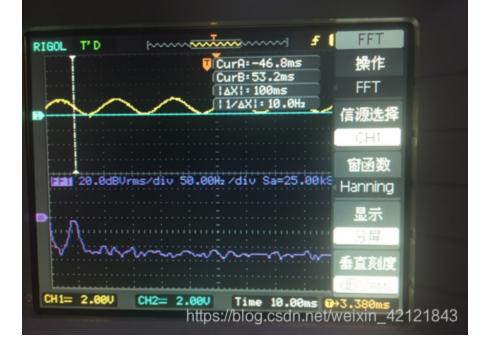

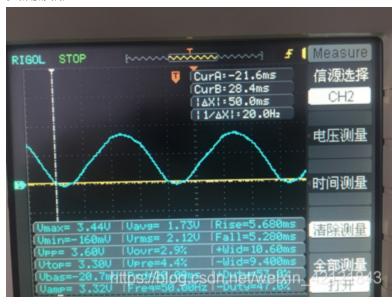

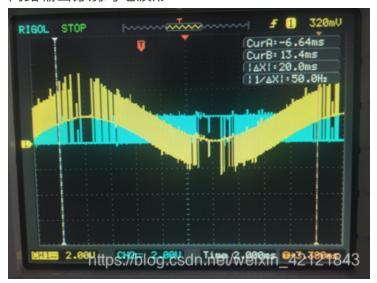

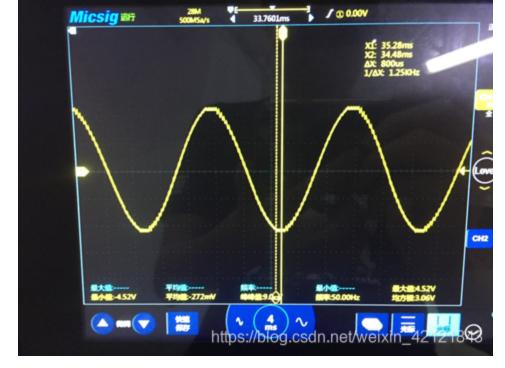

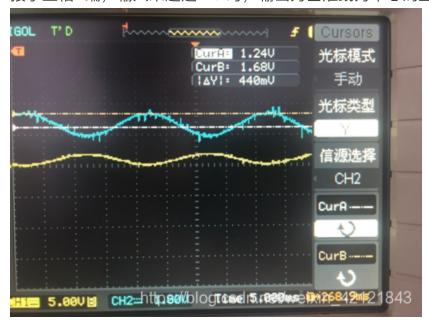

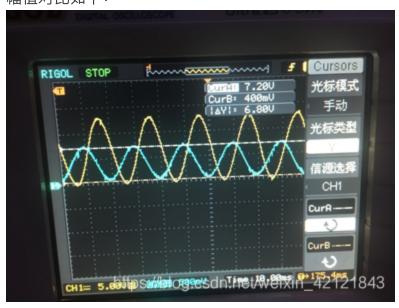

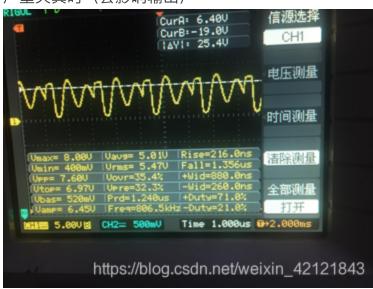

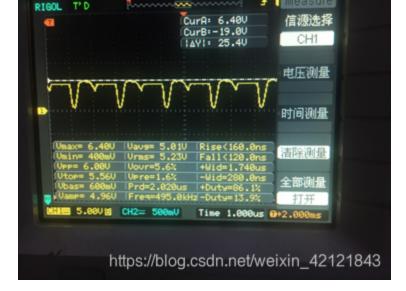

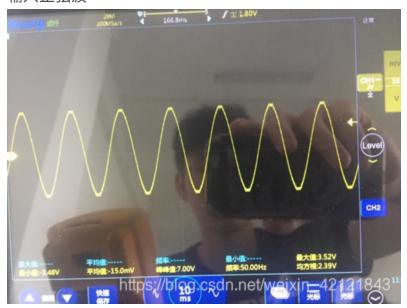

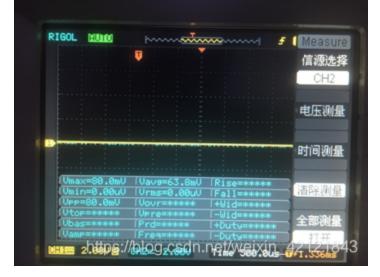

## 低通滤波不充分和充分时对比:

滤波器选择的时候,还要注意幅频特性和相频特性:在通带内相频和幅频曲线应平稳,否则会有失真,如 上图不规则的正弦波(黄色)

# 1.2有源滤波器

这里只记录低通和带通滤波器

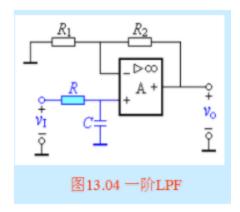

# 1.2.1 一阶低通

当f=0时,各电容器可视为开路,通带内的增益为:

$$A_{vp} = 1 + \frac{R_2}{R_1}$$

一阶低通滤波器的传递函数如下

$$A(s) = \frac{V_0(s)}{V_1(s)} = \frac{A_{vp}}{1 + \left(\frac{s}{\log s}\right) \log \frac{1}{s} \sin \frac{1}{s}}$$

,  $\sharp \Phi \omega_0 = \frac{1}{RC}$

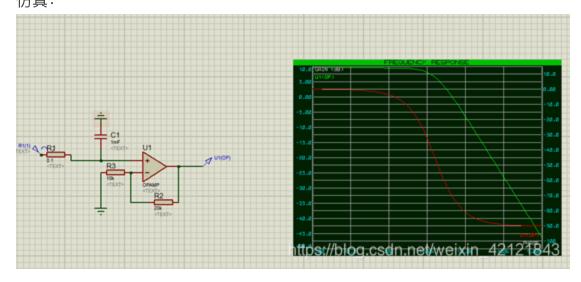

和无源滤波器相似,只是多了增益一项 仿真:

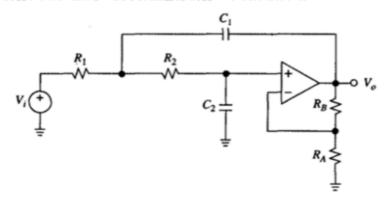

# 1.2.2 二阶低通

低通滤波器的设计是已知  $w_o$  (-3dB 截止频率)、 $H_{0LP}$  (直流增益)、Q (在-3dB 截止频率时的电压放大倍数与通带放大倍数数值之比)三个参数来设计电路,可选的电路形式为压控电压源低通滤波器和无限增益多路反馈低通滤波器。下面分别介绍:

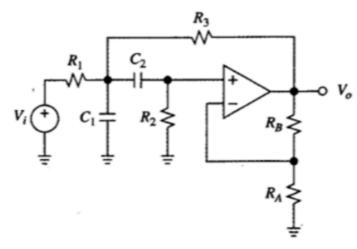

图 1 二阶压控电压源低通滤波器原理图

$$\begin{cases} H_{0LP} = K = 1 + \frac{R_B}{R_A} \\ W_o = \frac{1}{\sqrt{R_1 C_1 R_2 C_2}} \\ Q = \frac{1}{(1 - K)\sqrt{R_1 C_1 / R_2 C_2} + \sqrt{R_1 C_2 / R_2 C_1} + \sqrt{R_2 C_2 / R_1 C_1}} \end{cases}$$

由上式可知,可通过先调整  $R_1$  来先调整  $w_o$  ,然后通过调整 K 来调整 Q 值。

对于巴特沃斯、切比雪夫、贝塞尔三种类型二阶 LPF 的 Q 值分别为 0.707、1、0.56。 令R1=R2=R,C1=C2=C,则得出简化的设计:

$$\begin{cases}

RC = \frac{1}{w_o} \\

K = 3 - \frac{1}{Q} \\

R_B = (K - 1)R_A

\end{cases}$$

#### 仿真:

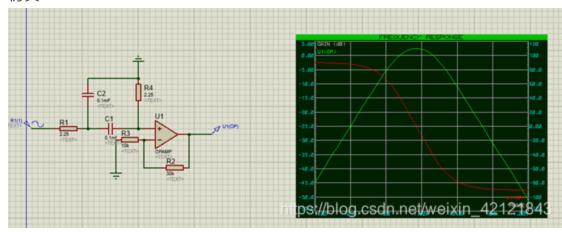

带通滤波器的设计是已知 $w_o$  (中心频率)、 $H_{0BP}$  (谐振增益)、Q ( $Q = \frac{f_0}{RP}$ ,

BP 为带通滤波器带宽)三个参数来设计电路,可选的电路形式为压控电压源带通滤波器和无限增益多路反馈带通滤波器。下面分别介绍:

图 4 二阶压控电压源带通滤波器原理图

$$\begin{cases} w_o = \frac{\sqrt{1 + R_1/R_3}}{\sqrt{R_1C_1R_2C_2}} \\ H_{0BP} = \frac{K}{1 + (1 - K)R_1/R_3 + (1 + C_1/C_2)R_1/R_2} \\ Q = \frac{\sqrt{1 + R_1/R_3}}{\left[1 + (1 - K)R_1/R_3\right]\sqrt{R_2C_2/R_1C_1} + \sqrt{R_1C_2/R_2C_1} + \sqrt{R_1C_1/R_2C_2}} \end{cases}$$

式中,

$$K=1+\frac{R_B}{R_A}$$

由上式可知,可通过先调整R,来先调整W。 然后通过调整K来调整Q值。

如果

$$Q>\sqrt{2}/3$$

, 令  $R_1=R_2=R_3=R$  和  $C_1=C_2=C$  ,简化上述各式,则

得出的设计方程为

$$\begin{cases} RC = \frac{\sqrt{2}}{w_o} \\ K = 4 - \sqrt{2}/Q \\ R_B = (K - 1)R_A \end{cases}$$

由上式可知, K值依赖于 Q值大小。

## 仿真:

# 1.3 全桥逆变SPWM滤波笔记

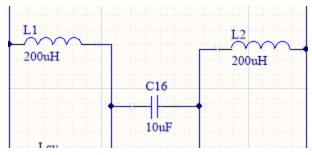

# 1.3.1 LCL滤波

### 原理图

### 波形

### 实验记录:

1.经查阅资料,该种滤波器数值难以计算,没有确定的公式,仿真也难以得出。故放弃此方案

### 附:谐振频率计算

1. 谐振频率的选择

为了滤除开关频率所产生的高频噪声,一般 L1与 Ci的谐振频率大多设计在小于系统开关频率的 1/10,且截至频率至 少大于十倍的基波频率如下式所示:

10 • f

$$\leq \frac{1}{2\pi\sqrt{L1C1}} \ll \frac{fx}{10}$$

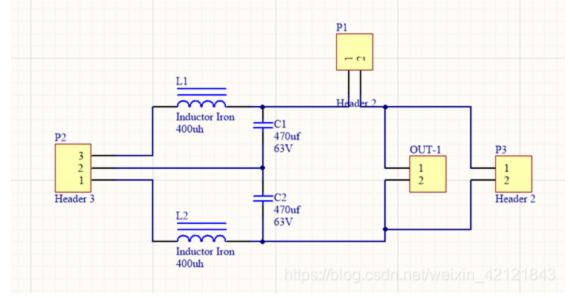

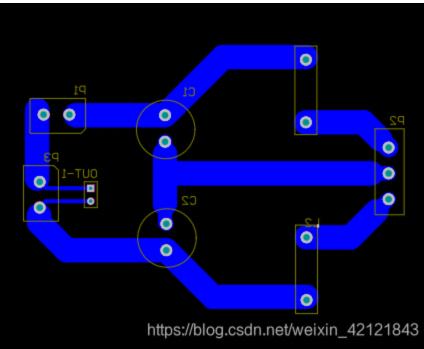

# 1.3.2 两路LC滤波

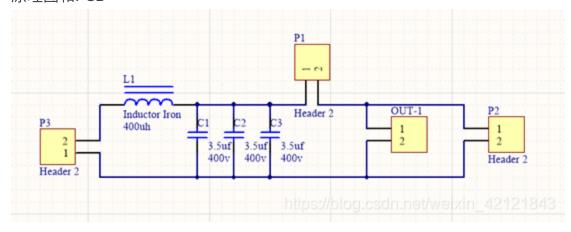

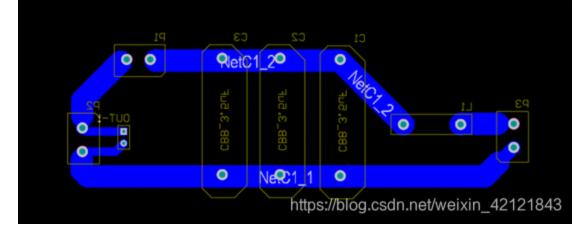

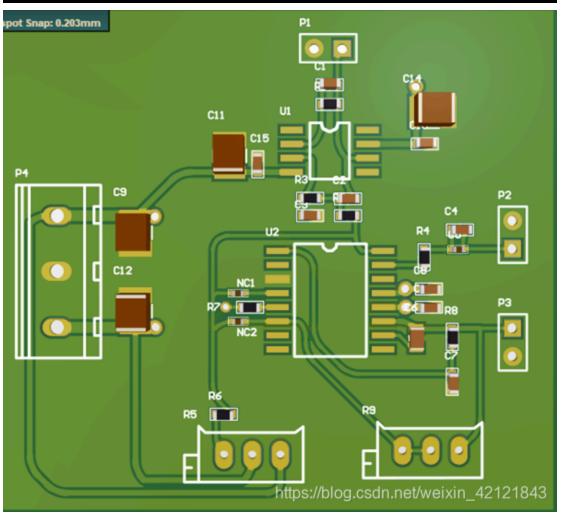

原理图和PCB:

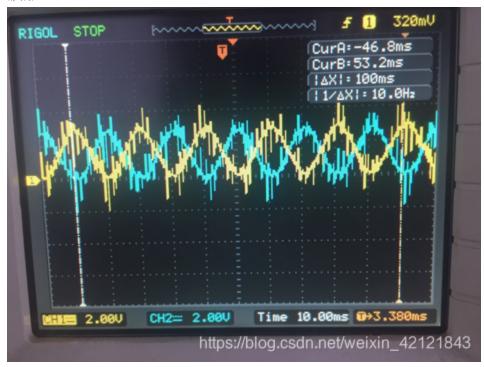

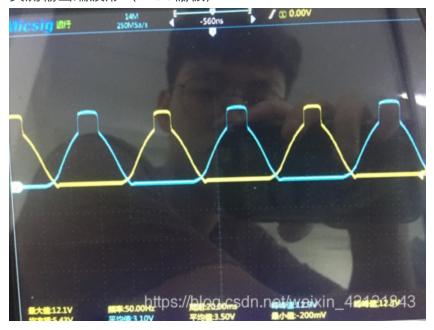

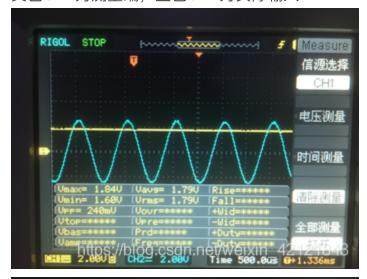

波形 对地波形,未接负载时:

接了负载后,谐波分量显著减少

## 两端波形:

效率:

| 遊     | 2十滤液效 | 中侧坑: 俊 | 新6.952)          | 电磁大    | ,DC和几端附右延大LI4V时 |

|-------|-------|--------|------------------|--------|-----------------|

| PC輸加  | l:    |        | : (檢爐)           | 级等:    | 有121岁           |

| 3.3V  | 0.23A | 2.14V  | The State of the | 81.8%  |                 |

| 6.DV  | 0.42A | 3.90V  | 0.56A            | 86.6%  |                 |

| 9.70  | 0.68A | 6.32V  | 0.91A            | 872%   |                 |

|       | 0.89A | 8.211  | 1-18A            | 1      |                 |

| 14.5V | 1.01A | 9.491  | 1.37A            | 88.8%. |                 |

### 实验记录:

1.电压加的很大时,DC输入有很大的跳变。分析原因是因为滤波模块的GND影响。

# 1.3.3 单路LC滤波

## 原理图和PCB

注意:此处使用的电容为无极性,高频特性好,耐高压的CBB电容

### 仿真如下:

负载一边为正弦,另一边为方波

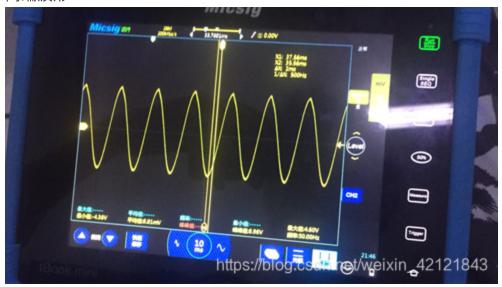

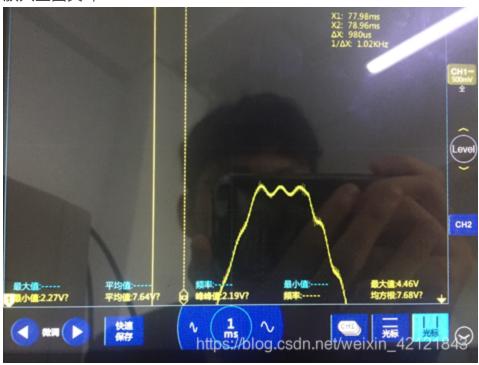

### 实测波形

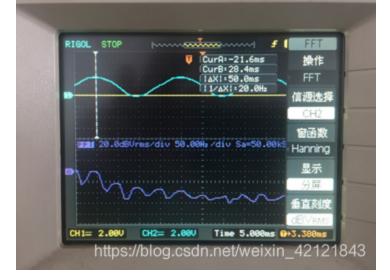

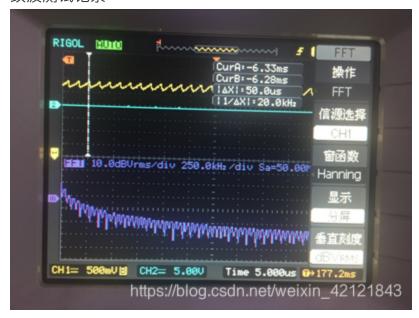

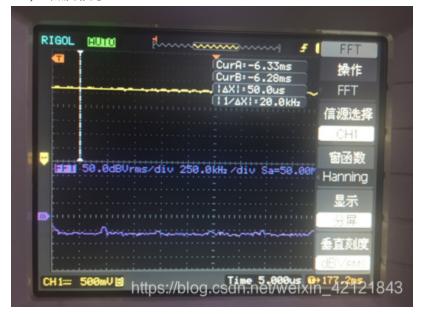

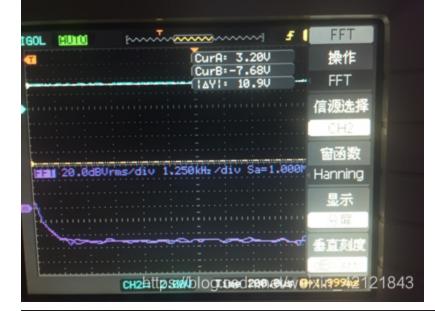

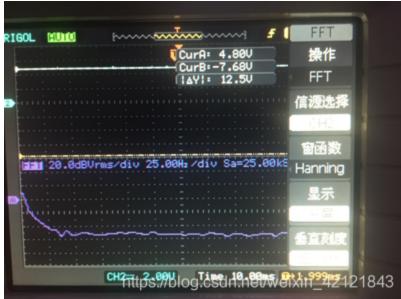

谐波成分如下:

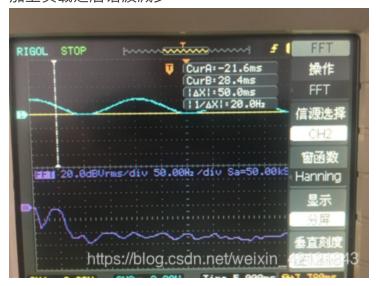

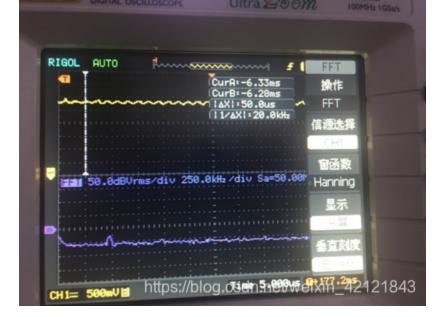

加上负载之后谐波减少

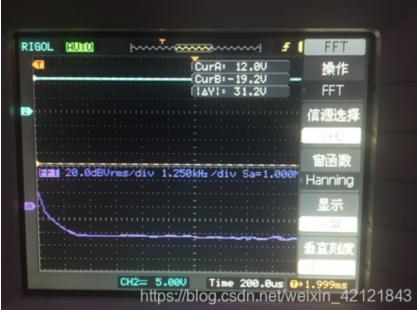

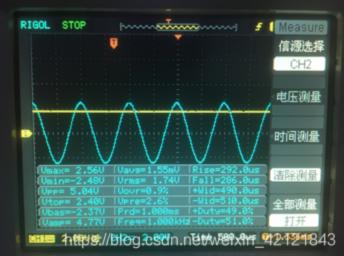

两路输出分别对地波形

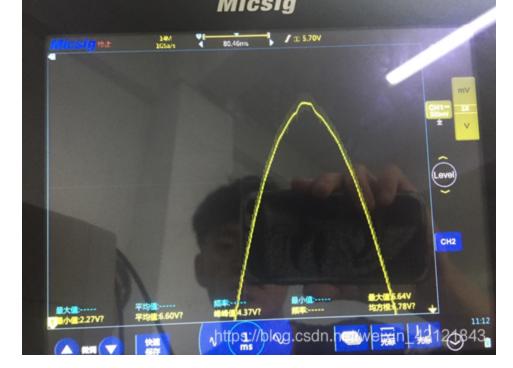

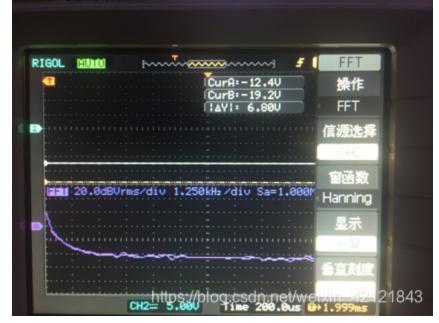

一路输出相对另一路输出的波形, 未接负载时

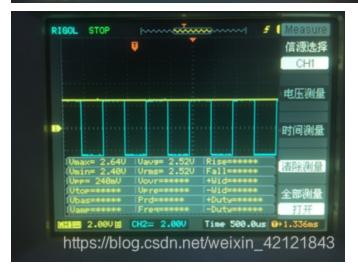

放大上图尖峰

接了负载之后谐波减少

## 实验记录:

- 1.DC输入端跳变减少,稳定了很多

- 2.效率测试为94左右,在20w左右。(全桥逆变加上滤波模块)

# 2.电流采样模块

芯片资料

使用说明↓

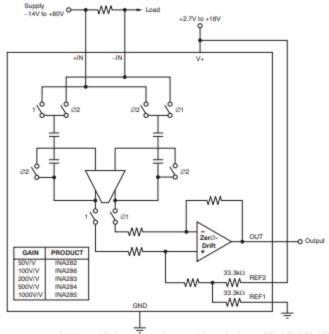

此芯片通过在+IN和-IN之间接入一个采样电阻(电阻值很小约0.01 Ω为宜)当有电阻上有电流流过时采样电阻上将会产生压降,通过+IN 与-IN口进入,再由芯片内部的差分放大,抑制共模信号放大差模信 号,由OUT口输出,通过REF1, REF2引脚控制输出模式。内部结构,与

INA282 的输出类型有三种即单向输出,双向输出,外部基准输出

# 单向输出(将 REF1 和 REF2 同时接到地或 V+端)

输出电压值随电流的增加而呈线性的增加或较小

# 双向输出(将 **REF1** 和 **REF2** 一端接 **GND**,另一端接 **V+**)

输出从 1/2V+ 为基准线性增加或较小

# 外部基准输出

https://blog.csdn.net/weixin\_42121843

#### INA282原理:

https://blog.csdn.net/weixin\_42121843

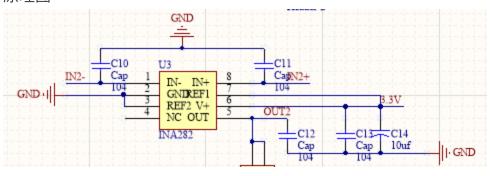

REF1接地, REF2接3.3v, 即输出的范围为0~3.3v

增益为50,则输出计算公式: V=U1+50RI,其中,R为采样电阻值,故这个电阻越小,采样范围越大。U1为基准电压,即电流为0时的输出值。输入负的电流时小于基准电压,输入正的电流时大于基准电压。输出最小为0,最大两倍基准电压。

#### 注意事项:

输入端一定要滤波, 否则杂波会严重影响精度

### 原理图:

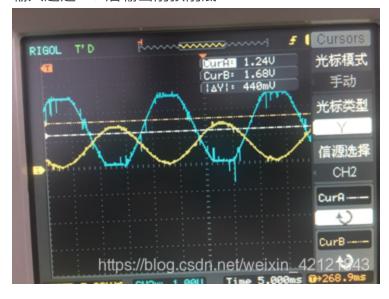

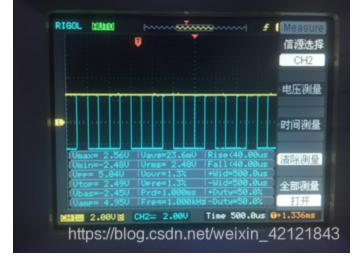

### 实测波形:

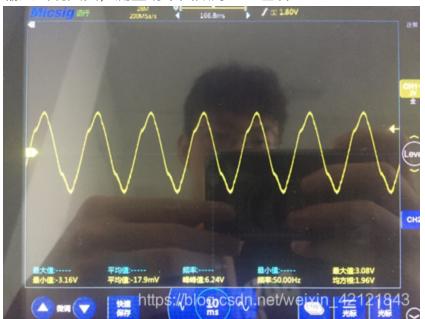

接于三相A端,输入未超过Vref时,输出为基准线为中心的正弦波。经测试,增益为50,非常准确

输入超过Vref后输出削顶削底

# 2.电压采样模块

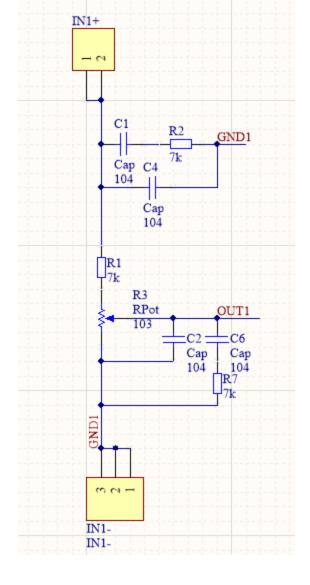

采用分压测量,比例由电位器决定。经测试,电流极小。

# 实测波形:

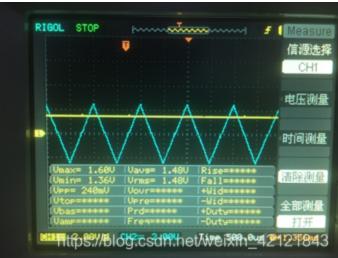

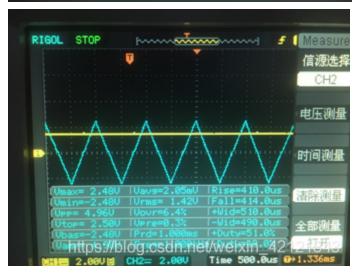

幅值对比如下:

经测试,该模块线性特性不是很好,不够精确,故采用更精确的AD芯片作为电压采样

# 3.辅助电源模块

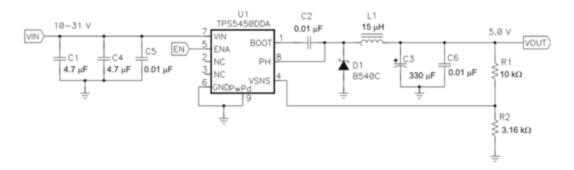

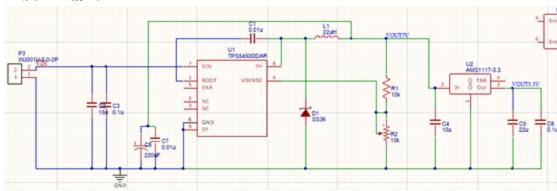

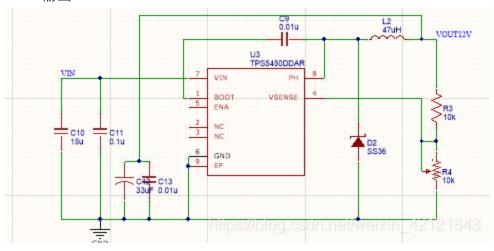

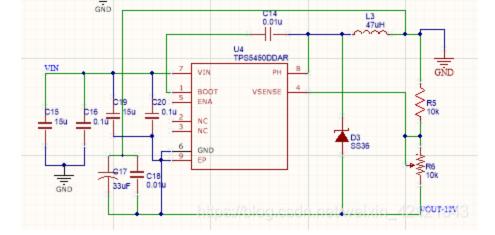

#### 芯片资料与原理图

采用AMS1117和TPS5450两种芯片,输入>12v,输出±12v,5v,3.3v。

典型连接: (以5v输出为例)

计算公式: (输出电压由VENSE的反馈决定)

$$R2 = \frac{R1 \times 1.221}{V_{OUT} - 1.221}$$

#### 5v及3.3v输出:

## +12v输出:

## -12v输出:

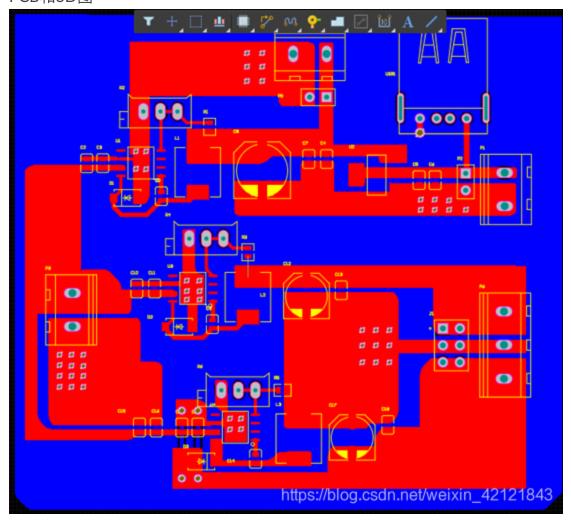

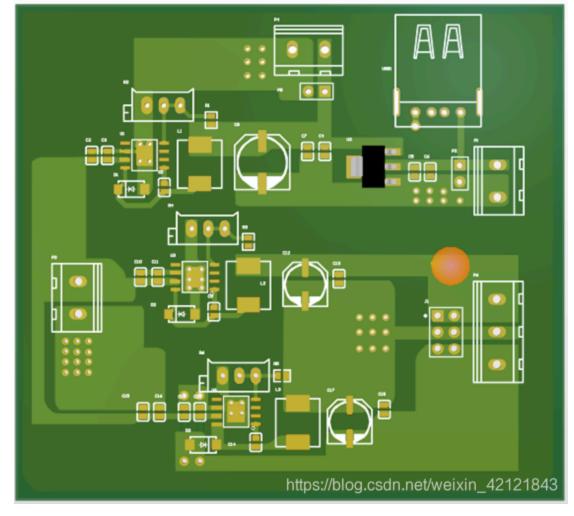

### PCB和3D图:

## 波形与分析

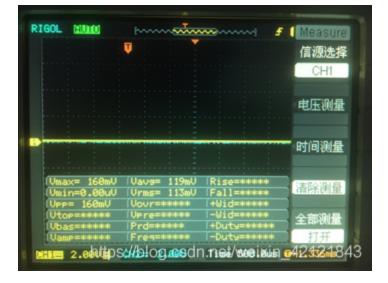

### 芯片输出波形

芯片测试记录:

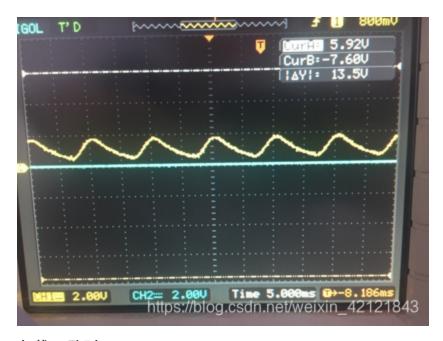

BOOT和PH输出高频信号(据芯片资料为500kHZ),电感电容应为LC滤波 芯片BOOT输出波形不正常时:需要检查芯片周围的电路是否正常,或者更换芯片。

## 严重失真时(会影响输出):

少许失真时 (不影响使用)

### 不失真时:

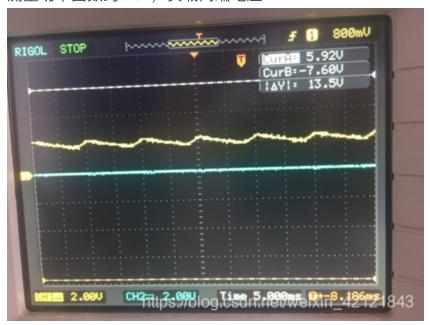

### 手制PCB直流输出波形:

### 纹波测试记录:

12v, 纹波大 (500mv左右), 且电压越大, 纹波越大

5v, 纹波较小

3.3V, 5v经过AMS1117后纹波进一步减少

# 厂家制作PCB直流输出波形:

纹波特性测试:

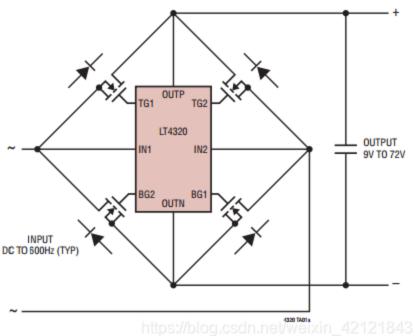

# 5. LT4320整流模块

芯片资料

典型连接:

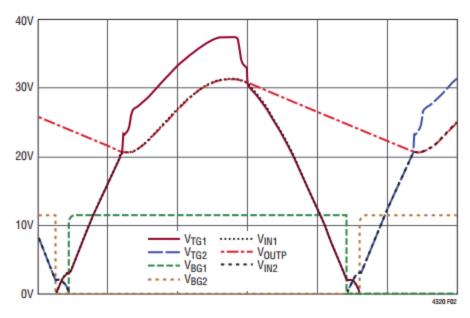

## 控制端输出波形示例:

Figure 2. 24V AC Sample Waveform | 12121843

## 桥式整流(全波整流计算):

交流电压的有郊值为U,全波整流后;一、当未加滤波电容时直流电压为:0.9U;二、当有滤波电容,但未 接入负载(空载)时直流电压为: 1.414U三、当有滤波电容,且接入了正常的负载后直流电压为: 1.2U

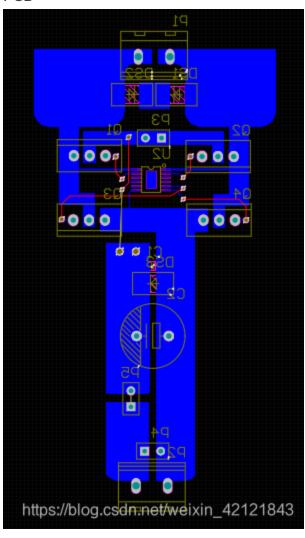

#### PCB:

## 实测输出端波形 (MOS栅极):

## 分析:

- 1.可见其控制端输出波形不规整,与输入有关,具体原理与芯片内部控制有关,无从得知

- 2.控制端有负电压,猜测是因为负电压可以使MOS管更彻底地关断

## 接负载时波形记录(输入50Hz正弦)

## 负载6.9欧时:

输入出现失真,测量功率因数为0.75左右

负载两端电压

负载50欧时:

# 测量功率因数约0.69,负载两端电压

无负载时(理想情况)

## 输入正弦波

输出直流

#### 波形分析:

1.输出纹波较大,经分析为滤波电容的问题。因频率低,负载小,滤波电容要大。这里选用的680uF偏小,要根据实际情况调整。整流滤波电容计算方法如下:

方法一:

$$R_LC \ge (3 \sim 5)\frac{T}{2}$$

#### 方法二:

桥式整流电路的滤波电容取值在工程设计中,一般由两个切入点来计算。

一是根据电容由整流电源充电与对负载电阻放电的周期,再乘上一个系数来确定的,另一个切入点是根据电源滤波输出的波纹系数来计算的,无论是采用那个切入点来计算滤波电容都需要依据桥式整流的最大输出电压和电流这两个数值。 通常比较多的是根据电源滤波输出波纹系数这个公式来计算滤波电容。

- C》 0.289/{fx (U/I) ×ACv}

- C,是滤波电容,单位为F。

- 0.289,是由半波阻性负载整流电路的波纹系数推演来的常数。

- f, 是整流电路的脉冲频率, 如 50Hz交流电源输入, 半波整流电路的脉冲频率为 50Hz, 全波整流电路的脉冲频率为 100Hz。单位是 Hz。

- U,是整流电路最大输出电压,单位是 V。

- I,是整流电路最大输出电流,单位是 A。

ACv,是波纹系数,单位是%。

(咦~没赏分的? 汗~)

例如,桥式整流电路,输出 12V, 电流 300mA, 波纹系数取8%, 滤波电容为:

C》 0.289/{100Hz×(12V/0.3A)×0.08} https://blog.csdn.net/weixin\_42121843

正弦工频AC输入时测试数据:(估计效率96以上)

| 13.5V 0.94  |            | 2.691 16.7  | V 05/A   |            |

|-------------|------------|-------------|----------|------------|

| 12.1 . 1.12 | A 11.900   | 1,692 18.7  | V OBOR   | A 14 m # / |

| 17.5V 1.25  |            | 692   21.   | OV 0.66A | 1, .1      |

| 20.21 1.42  |            |             |          | 1 4:       |

| 22.6V 1.61. | A 25.210 0 | 1.692   27: | 2V 0.87  | 19. /      |

## 实验记录:

1.万用表误差极大,示波器误差小很多。

2.mos管几乎不发热

# 与二极管整流对比:

| 整流析效(全波、5556=柳筍): A C核似(放射),加手成为))                                                | 4.948<br>*被AC模拟: C模拟).               | 対し                     |

|-----------------------------------------------------------------------------------|--------------------------------------|------------------------|

| 8.0V (10)4A 8.3W<br>10.8V 1.408A 15.4W<br>12.3V (1.613 20.0W<br>13.8V 1.804 25,0W | 7.08V<br>9.74V<br>11.2V<br>12.5V     | 86.6%                  |

| 15. N [.98] 30. W                                                                 | 13.81/<br>https://blog.csdn.net/weix | 19/16/<br>kin_42/21848 |

## 实验记录:

1.二极管发热严重,长时间工作可能需要散热片

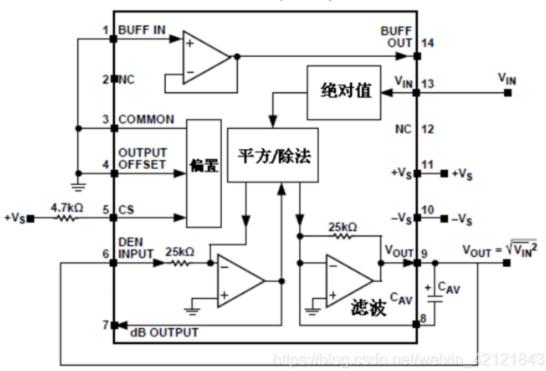

# 6. AD637有效值测量模块

### AD637 (DIP14)

| Pin No. | Mnemonic        | Description                    |  |  |  |  |

|---------|-----------------|--------------------------------|--|--|--|--|

| 1       | BUFF IN         | Buffer Input                   |  |  |  |  |

| 2, 12   | NIC             | No Internal Connection         |  |  |  |  |

| 3       | COMMON          | Analog Common                  |  |  |  |  |

| 4       | OUTPUT OFFSET   | Output Offset                  |  |  |  |  |

| 5       | CS              | Chip Select                    |  |  |  |  |

| 6       | DEN INPUT       | Denominator Input              |  |  |  |  |

| 7       | dB OUTPUT       | dB Output                      |  |  |  |  |

| 8       | C <sub>AV</sub> | Averaging Capacitor Connection |  |  |  |  |

| 9       | RMS OUT         | RMS Output                     |  |  |  |  |

| 10      | -V <sub>s</sub> | Negative Supply Rail           |  |  |  |  |

| 11      | +Vs             | Positive Supply Rail           |  |  |  |  |

| 13      | V <sub>IN</sub> | Signal Input                   |  |  |  |  |

| 14      | BUFF OUT OG.C   | Buffer Output XIII_42121843    |  |  |  |  |

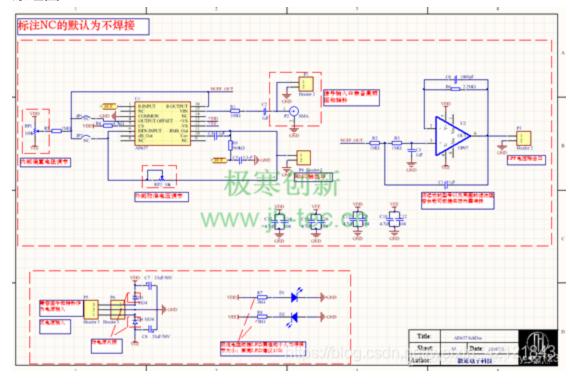

## 原理图:

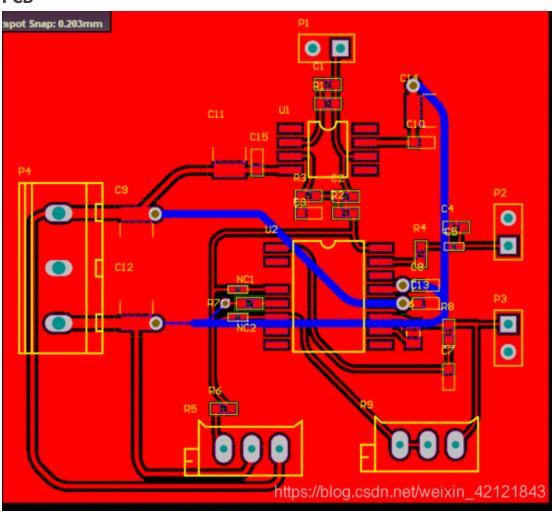

### **PCB**

## 波形记录:

$V_{OUT} = \frac{{V_{IN}}^2}{V_{DEN}}$

分母输入端短接了, 因为:

,若想输出等于输入,则Vden直接接输出端

黄色CH1为测量端,蓝色CH2为实际输入:

#### 波形分析:

1.可见测量值与实际值相差很小,因示波器的AD是8位的,无法得知其精准的值,故两个波形的有效值仍然相差一个很小的值

2.该模块可以很大程度上弥补瞬时测量和峰值检波等方法测量有效值的不足,因为其采用了积分的方式,即使波形不规整,谐波大,也可以得到有效值。

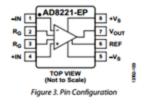

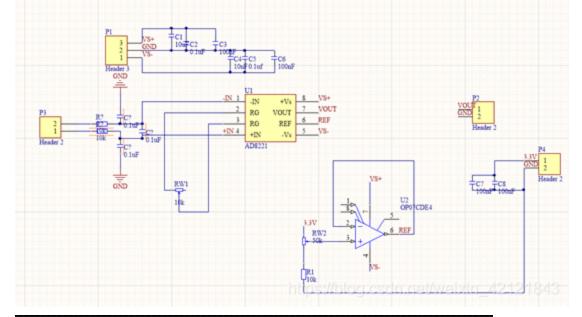

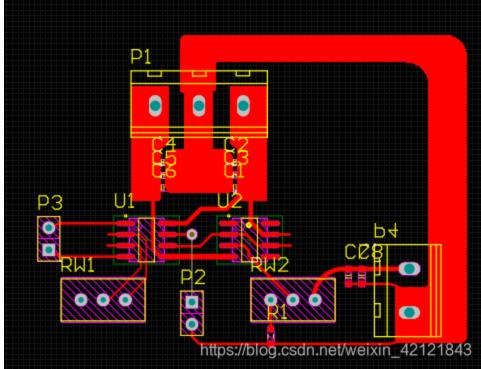

# 7. AD8221差分放大模块

### 芯片资料

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                         |  |  |  |  |  |  |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1       | -IN      | Negative Input Terminal.                                                                                                            |  |  |  |  |  |  |

| 2,3     | Ra       | Gain Setting Terminal. Place resistor across the R <sub>6</sub> pins to set the gain. $G = 1 + (49.4 \text{ k}\Omega/\text{R}_6)$ . |  |  |  |  |  |  |

| 4       | +IN      | Positive Input Terminal.                                                                                                            |  |  |  |  |  |  |

| 5       | -Vs      | Negative Power Supply Terminal.                                                                                                     |  |  |  |  |  |  |

| 6       | REF      | Reference Voltage Terminal. Drive this terminal with a low impedance voltage source to level-shift the output                       |  |  |  |  |  |  |

| 7       | Vour     | Output Terminal.                                                                                                                    |  |  |  |  |  |  |

| 8       | +Vs      | Positive Power Supply Terminal.                                                                                                     |  |  |  |  |  |  |

#### 原理图和PCB

## 实验记录

1.经测量,精度很高,符合芯片描述

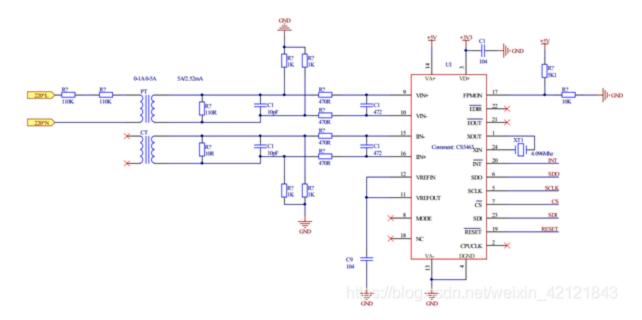

# 8. CS5463功率测量模块

## 芯片资料和原理图:

片内功能:

- ——可以测量瞬时电压,电流和功率: IRMS和 VRMS, 视在功率,有功和无功功率: 有功的基波和谐波功: 无功的基波功率,功率因数,频率

- ——具有电能-脉冲转换功能

- ——具有系统校准和相位补偿

- ——具有温度传感器

| Constal Out                | VOLIT     | 7 | 1.0   | 24 | L | VIN   | Constal la                   |

|----------------------------|-----------|---|-------|----|---|-------|------------------------------|

| Crystal Out                | XOUT      | 9 | 1 ● ~ | 24 | Р | XIN   | Crystal In                   |

| CPU Clock Output           | CPUCLK    | d | 2     | 23 | þ | SDI   | Serial Data Input            |

| Positive Digital Supply    | VD+       | d | 3     | 22 | þ | E2    | Energy Output 2              |

| Digital Ground             | DGND      | d | 4     | 21 | þ | E1    | Energy Output 1              |

| Serial Clock               | SCLK      | d | 5     | 20 | þ | INT   | Interrupt                    |

| Serial Data Ouput          | SDO       | d | 6     | 19 | þ | RESET | Reset                        |

| Chip Select                | <u>cs</u> | d | 7     | 18 | þ | E3    | High Frequency Energy Output |

| Mode Select                | MODE      | d | 8     | 17 | þ | PFMON | Power Fail Monitor           |

| Differential Voltage Input | VIN+      | d | 9     | 16 | þ | IIN+  | Differential Current Input   |

| Differential Voltage Input | VIN-      | d | 10    | 15 | þ | IIN-  | Differential Current Input   |

| Voltage Reference Output   | VREFOUT   | d | 11    | 14 | þ | VA+   | Positive Analog Supply       |

| Voltage Reference Input    | VREFIN    | d | 12    | 13 | þ | AGND  | Analog Ground                |

|                            |           | L |       |    | J |       |                              |

| Clock Generator              |          |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Crystal Out<br>Crystal In    | 1,24     | OUT, XIN - The output and input of an inverting amplifier. Oscillation occurs when connected to<br>rystal, providing an on-chip system clock. Alternatively, an external clock can be supplied to<br>XIN pin to provide the system clock for the device.                                                        |  |  |  |  |  |

| CPU Clock Output             | 2        | CPUCLK - Output of on-chip oscillator which can drive one standard CMOS load.                                                                                                                                                                                                                                   |  |  |  |  |  |

| Control Pins and Serial Data | I/O      |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Serial Clock Input           | 5        | $ \textbf{SCLK} - \textbf{A Schmitt-Trigger input pin. Clocks data from the SDI pin into the receive buffer and out of the transmit buffer onto the SDO pin when \overline{\text{CS}} is low.  $                                                                                                                |  |  |  |  |  |

| Serial Data Output 6         |          | SDO -Serial port data output pin.SDO is forced into a high-impedance state when $\overline{\text{CS}}$ is high.                                                                                                                                                                                                 |  |  |  |  |  |

| Chip Select                  | 7        | CS - Low, activates the serial port interface.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Mode Select                  | 8        | MODE - High, enables the "auto-boot" mode. The mode pin has an internal pull-down resistor.                                                                                                                                                                                                                     |  |  |  |  |  |

| Energy Output                | 18,21,22 | E3, E1, E2 - Active-low pulses with an output frequency proportional to the selected power. Configurable outputs for active, apparent, and reactive power, negative energy indication, zero cross detection, and power failure monitoring. E1, E2, E3 outputs are configured in the Operational Modes Register. |  |  |  |  |  |

| Reset                        | 19       | RESET - A Schmitt-Trigger input pin. Low activates Reset, all internal registers (some of which drive output pins) are set to their default states.                                                                                                                                                             |  |  |  |  |  |

| Interrupt                    | 20       | INT - Low, indicates that an enabled event has occurred.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Serial Data Input            | 23       | SDI - Serial port data input pin. Data will be input at a rate determined by SCLK.                                                                                                                                                                                                                              |  |  |  |  |  |

| Analog Inputs/Outputs        |          |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Differential Voltage Inputs  | 9,10     | VIN+, VIN Differential analog input pins for the voltage channel.                                                                                                                                                                                                                                               |  |  |  |  |  |

| Differential Current Inputs  | 15,16    | IIN+, IIN Differential analog input pins for the current channel.                                                                                                                                                                                                                                               |  |  |  |  |  |

| Voltage Reference Output     | 11       | <b>VREFOUT</b> - The on-chip voltage reference output. The voltage reference has a nominal magnitude of 2.5 V and is referenced to the AGND pin on the converter.                                                                                                                                               |  |  |  |  |  |

| Voltage Reference Input      | 12       | VREFIN - The input to this pin establishes the voltage reference for the on-chip modulator.                                                                                                                                                                                                                     |  |  |  |  |  |

| Power Supply Connections     |          |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Positive Digital Supply      | 3        | VD+ - The positive digital supply.                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Digital Ground               | 4        | DGND - Digital Ground.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Positive Analog Supply       | 14       | VA+ - The positive analog supply.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Analog Ground                | 13       | AGND - Analog ground.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Power Fail Monitor           | 17       | PFMON - The power fail monitor pin monitors the analog supply. If the analog supply does not meet or falls below PFMON's voltage threshold, a Low-supply Detect (LSD) event is set in the status register.                                                                                                      |  |  |  |  |  |

# 实验记录:

1.经串口返回的数据,测量精准,符合芯片描述